新闻资讯

9422/9424/9428型延迟信号发生器

Quantum Composers 9420系列延迟信号发生器

时序逻辑测试

- 在数字电路中,时序逻辑电路(如触发器、计数器等)的正常工作依赖于时钟信号和数据信号之间的正确时序关系。Quantum Composers 9420系列延迟信号发生器可以产生具有精确延迟的时钟信号。例如,在测试D触发器时,通过该信号发生器可以设置时钟信号相对于数据输入信号的延迟时间。正常情况下,D触发器会在时钟信号的上升沿或下降沿将数据输入端的值传输到输出端。通过改变时钟信号的延迟,可以模拟不同的时序情况,如建立时间和保持时间违规的情况。

- 建立时间是指在时钟沿到来之前,数据信号必须保持稳定的时间;保持时间是指在时钟沿到来之后,数据信号必须保持稳定的时间。如果这两个时间要求得不到满足,触发器可能会出现错误的输出。利用延迟信号发生器,可以精确地控制时钟和数据信号的相对延迟,从而测试D触发器在各种时序条件下的性能,确定其能够正常工作的时序范围。

高速数字电路测试

- 对于高速数字电路(如高速微处理器、高速FPGA等),信号的传输延迟会对电路性能产生重大影响。9420系列延迟信号发生器可以生成纳秒级甚至皮秒级精度的延迟脉冲序列。在测试高速数字电路的内部通信线路时,比如片内总线或者高速串行接口,通过调整信号延迟来模拟信号在不同长度的线路或者不同负载条件下的传输情况。

- 例如,在测试高速串行通信接口(如PCI - Express接口)时,发送端和接收端对信号的时序要求非常严格。延迟信号发生器可以产生带有不同延迟的发送信号,来模拟信号在长距离传输或者经过复杂的电路板布线后的延迟变化。接收端需要能够正确地识别和恢复这些带有延迟的信号,通过这种测试可以评估接收端的时钟恢复和数据采样电路的性能,确保高速数字电路在实际应用中的可靠性。

数字信号完整性测试

- 在数字电路中,信号完整性是指信号在传输过程中能够保持其正确的波形和时序的特性。当信号在电路板上的走线中传输时,会受到反射、串扰等因素的影响,导致信号的延迟和波形畸变。9420系列延迟信号发生器可以模拟这些受干扰后的信号延迟情况。

- 例如,在测试一个包含多个数字信号的印刷电路板(PCB)时,可以使用延迟信号发生器在信号源端对其中一个信号添加延迟,模拟该信号受到串扰或者走线过长导致的延迟。然后观察其他信号以及整个数字电路系统的响应情况,检查是否会出现信号误判、数据丢失等问题。通过这种方式,可以评估PCB设计的信号完整性,并采取相应的措施(如调整走线布局、添加终端匹配电阻等)来改善信号传输质量。

数字电路故障诊断

- 当数字电路出现故障时,信号的时序错误往往是一个重要原因。9420系列延迟信号发生器可以帮助定位故障。例如,如果一个数字系统中的某个功能模块出现异常,通过在该模块的输入信号上逐步调整延迟时间,同时观察输出信号的变化情况,可以判断故障是否与信号的延迟有关。

- 假设一个数字计数器在计数过程中出现错误,可能是由于时钟信号或者复位信号的延迟异常导致的。使用延迟信号发生器对时钟信号和复位信号分别添加不同的延迟,观察计数器的输出行为,与正常情况下的计数序列进行对比,从而确定是哪个信号的延迟问题导致了故障,为后续的故障修复提供有力的线索。

Quantum Composers 9420系列延迟信号发生器欢迎咨询长春博盛量子,0431-85916189

高光谱/多光谱成像

高光谱/多光谱成像  光路调节相关

光路调节相关  光学频率梳相关

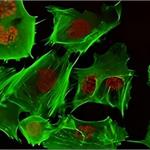

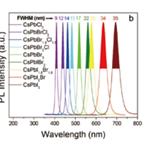

光学频率梳相关  荧光

荧光  光学组件

光学组件  激光器|光源

激光器|光源  拉曼测量

拉曼测量  Libs激光诱导击穿

Libs激光诱导击穿  显微光谱测量

显微光谱测量  量子效率

量子效率  9420数字延迟脉冲信号发生器

9420数字延迟脉冲信号发生器